文章编号:1004-2474(2022)02-0260-04

**DOI:** 10. 11977/j. issn. 1004-2474, 2022, 02. 022

# C 波段 WLP 薄膜体声波滤波器的研制

刘 娅1,2,孙 科1,马晋毅2,谢征珍2,蒋平英2,杜雪松2

(1. 电子科技大学 材料与能源学院,四川 成都 610054;2. 中国电子科技集团公司第二十六研究所,重庆 400060)

摘 要:该文研制了一种晶圆级封装(WLP)的 C 波段薄膜体声波谐振器(FBAR)滤波器。采用一维 Mason 等 效电路模型对谐振器进行设计,并使用 HFSS 对电磁封装模型进行优化,再在 ADS 中对滤波器进行仿真优化设 计,得到阶梯型结构的 FBAR 滤波器。采用空腔型结构并制备出 FBAR 滤波器芯片,同时利用覆膜工艺对 FBAR 裸 芯片进行覆膜和电镀等 WLP 工艺,得到 WLP 的 FBAR 器件。测试结果表明,滤波器的中心频率为 6.09 GHz,中心 插损为 2.92 dB,通带插损为 3.4 dB,带宽为 112 MHz,带外抑制大于 40 dB。

关键词:薄膜体声波谐振器(FBAR); Mason模型; 晶圆极封装(WLP); 覆膜; 插入损耗

中图分类号:TN65 文献标志码:A

# Development of C Band WLP Packaged FBAR

LIU Ya<sup>1,2</sup>, SUN Ke<sup>1</sup>, MA Jinyi<sup>2</sup>, XIE Zhengzhen<sup>2</sup>, JIANG Pingying<sup>2</sup>, DU Xuesong<sup>2</sup>

(1. University of Electronic Science and technology of China, Chengdu 610054, China;

2. The 26th Institute of China Electronic Technology Group Corporation, Chongqing 400060, China)

Abstract: A C band thin film bulk acoustic resonator(FBAR) filter packaged by WLP was developed in this paper. The one-dimensional Mason equivalent circuit model was used to design the resonator, the HFSS was used to optimize the electromagnetic packaging model, and then the filter was simulated and optimized in ADS to obtain the stepped FBAR filter. FBAR filter chip was fabricated by cavity structure, and WLP was carried out by taping and electroplating on FBAR bare chip. The test results showed that the center frequency of the filter was 6.09 GHz, the center insertion loss was 2.92 dB, the passband insertion loss was 3.4 dB, the bandwidth was 112 MHz, and the out-of-band rejection was greater than 40 dB.

Key words; film bulk acoustic resonator (FBAR); Mason model; wafer level package (WLP); tape; insertion loss

### 引言

随着电子整机装备系统和移动通信技术的飞速 发展,通信频段进一步向高频(S和C波段)扩展,相 控阵雷达、电子对抗和通信系统对高频滤波器的性 能和体积提出了更高要求[1],市场对滤波器性能的 要求也越来越严格;同时,5G 通信技术中通信频段 将进一步向高频高性能扩展,随着通讯频段的增加, 一个通讯设备里需放入多个滤波器,因此对滤波器 芯片的封装尺寸提出了更高的要求。

薄膜体声波谐振器(FBAR)滤波器封装从传统的 表面贴装封装(SMD,其最小尺寸3 mm×3 mm)到芯 片级封装(CSP,其尺寸为 1.1 mm×0.9 mm)[2],而采 用晶圆级封装(WLP)的尺寸可达到芯片尺寸大小。 WLP采用专用贴膜设备首先在芯片表面贴一层聚 酰亚胺(PI)膜,把谐振器区域裸露出来,再在第一层 膜上贴另一种 PI 膜,使谐振器区域形成空腔以利于

谐振,同时在焊盘区域露出用于电镀引线的区域,最 后通过电镀和刷球完成封装,封装后的尺寸和芯片 尺寸保持一致[3-4]。WLP做C波段FBAR滤波器 的成功研制,可以满足电子整机系统、通信设备和模 组集成对滤波器高频小体积的要求。但由于 FBAR 滤波器是带有空腔的结构,在覆膜时空腔结构易塌 陷或薄膜破裂[5],从而使滤波器性能恶化,甚至失 效[6]。因此,研制小型化高频的 FBAR 滤波器对当 前及未来武器装备和移动通信的发展具有非常重要 的意义。

#### 1 FBAR 滤波器的设计

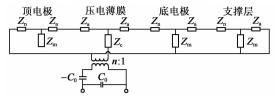

本文采用一维 Mason 模型来仿真谐振器的频 率特性,其等效电路如图 1 所示。FBAR 由支撑层、 下电极、压电层、上电极组成,种子层和保护层的边 界均为空气界面,以限制声波能量在谐振器结构中。 压电层有 2 个声学端口和 2 个电学端口,普通声学 层具有 2 个声学端口。将压电层、普通声学层的等效电路级联,得到常规 FBAR 的 Mason 等效电路。图中, $Z_a$ , $Z_a$ , $Z_m$ , $Z_c$ 为阻抗, $C_o$ 为电容

图 1 Mason 等效电路图

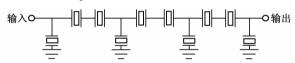

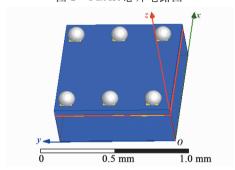

采用 ADS 软件进行建模,该 FBAR 滤波器采用阶梯型电路结构,如图 2 所示。由于 C 波段频率较高,对电容和电感敏感,FBAR 滤波器采用阻抗元结构,对互联通孔的大小和厚度等对器件的性能影响都很大。因此,在 HFSS 中根据通孔大小、厚度和球等建立 WLP 的电磁模型,如图 3 所示,同时进行有限元仿真,得到滤波器 WLP 的外围电磁参数。再根据滤波器的性能指标进行电磁仿真优化,确定各膜层的厚度和各个谐振器的面积和图形尺寸为1 mm×1 mm。

图 2 FBAR 芯片电路图

图 3 WLP 封装的 HFSS 模型

#### 2 FBAR 滤波器的制备

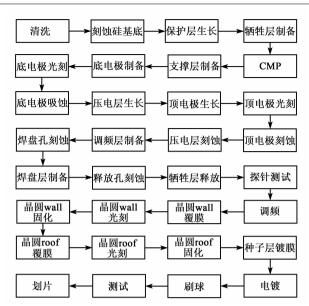

本文采用高阻硅片进行制作 FBAR 滤波器,有 机感光膜作为封帽材料,工艺流程如图 4 所示。图 中,wall 为搭腔体的墙,roof 为封闭腔体的层顶, CMP 为化学机械抛光。由于该 FBAR 滤波器采用 空腔型结构,在覆膜过程中,空腔结构易塌陷。因 此,在覆膜时需采用合适的工艺参数,在空腔不塌陷 的同时保证附着力<sup>[5]</sup>。为了使电镀填孔时孔内不产 生空洞或气泡,通孔的侧壁形貌需有一定角度,保证 电镀的质量,研究了覆膜后光刻条件对侧壁形貌的 影响,光刻实验方案如表 1 所示。

图 4 FBAR 滤波器 WLP 工艺流程图 表 1 光刻实验方案

| X 1                        | 儿刈天担刀朱 |          |

|----------------------------|--------|----------|

| 曝光量/(mJ·cm <sup>-2</sup> ) | 烘烤温度/℃ | 烘烤时间/min |

| 100                        | 100    | 2        |

| 100                        | 100    | 3        |

| 100                        | 100    | 4        |

| 100                        | 110    | 2        |

| 100                        | 110    | 3        |

| 100                        | 110    | 4        |

| 100                        | 120    | 2        |

| 100                        | 120    | 3        |

| 100                        | 120    | 4        |

| 200                        | 100    | 2        |

| 200                        | 100    | 3        |

| 200                        | 100    | 4        |

| 200                        | 110    | 2        |

| 200                        | 110    | 3        |

| 200                        | 110    | 4        |

| 200                        | 120    | 2        |

| 200                        | 120    | 3        |

| 200                        | 120    | 4        |

| 300                        | 100    | 2        |

| 300                        | 100    | 3        |

| 300                        | 100    | 4        |

| 300                        | 110    | 2        |

| 300                        | 110    | 3        |

| 300                        | 110    | 4        |

| 300                        | 120    | 2        |

| 300                        | 120    | 3        |

| 300                        | 120    | 4        |

## 3 结果与讨论

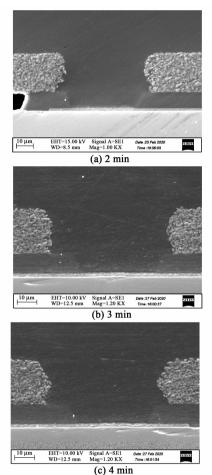

图 5 为不同烘烤时间显影后效果图。由图可知,随着烘烤时间的增加,孔内形貌从倒梯形逐渐变为子弹头形状;因为当烘烤时间不足时,显影后会呈现倒梯形状,烘烤时间过长显影后呈正梯形状。

图 5 不同烘烤时间显影后效果图

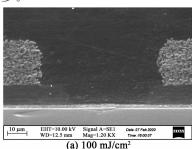

图 6 为不同曝光量显影后效果图。由图可知,随着曝光量的逐渐增加,显影后的残留也逐渐增多;由于该有机感光膜呈负性光刻胶性质,所以,随着曝光量的增大,底部反射增强,使底部不需曝光区域也被反射光曝光,导致底部显影残留的现象,曝光量越大残留越多。

(c) 300 mJ/cm<sup>2</sup> 图 6 不同曝光量显影后效果图

EHT=10.00 kV Signal A=SE1 WD=10.5 mm Mag=1.20 KX

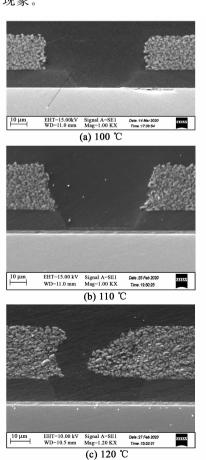

图 7 为不同烘烤温度显影后效果图。由图可知,随着烘烤温度逐渐增加,孔内形貌从垂直逐渐变

为倒梯形;当烘烤温度过高时,会导致过烘显影后出现残留的现象。

图 7 不同烘烤温度显影后效果图

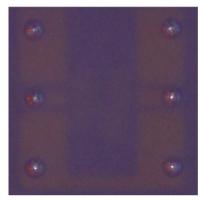

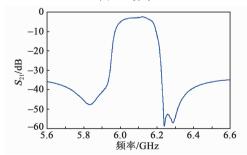

图 8 为 WLP 封装 FBAR 芯片图。由图可知,所有焊盘(PAD)通过通孔和锡球互连,给测试造成一定难度,芯片需焊接在电路板上才能测试,但是焊接在电路板上后该器件不能使用。所以,本文采用订制探卡(见图 9)通过探针的方法进行测试,可避免因测试导致器件报废。通过探卡测试后的曲线如图 10 所示。由图可以看出,滤波器的中心频率为6.09 GHz,中心插损为2.92 dB,通带插损为3.4 dB,带宽为112 MHz,带外抑制大于40 dB。通过测试结果可以看出,WLP 封装后滤波器的性能正常。

图 8 WLP 封装 FBAR 芯片图

图 9 探卡

图 10 WLP 封装后 FBAR 滤波器测试图

#### 4 结束语

本文介绍了一款 WLP 封装的 C 波段 FBAR 滤

波器。采用 Mason 模型对 FBAR 滤波器进行仿真, 采用 HFSS 对封装进行电磁环境仿真,并在 ADS 软件中进行滤波器芯片和电磁环境的联合仿真。为了 实现电镀填孔无空洞和气泡,对通孔形貌进行了实 验和优化,最后得到利于电镀填孔的倒梯形形貌,最 终得到 WLP 封装的 FBAR 滤波器。通过测试结果 发现器件性能满足指标要求。

#### 参考文献:

- [1] TSUTSUMI J, IWAKI M, MATSUDA T, et al. Advanced design echnologies for SAW/FBAR devices [C]//Keyaki Hall: International Symposium on AcousticWave Devices for Future Mobile Communication Systems, 2015:84-90.

- [2] TOPPER M, FISCHER T, BAUMGARTNER T, et al. A comparison of thin film polymers for wafer level packaging[C]//Las Vegas, NV:60th Electronic Components and Technology Conference, 2010:769-776.

- [3] 冷俊林,杨静,毛海燕,等.一种声表面波器件的新型晶圆级封装技术[J]. 压电与声光,2011,33(4):517-519. LENG Junling,YANG Jing,MAO Haiyan,et al. Anovel wafer level package technology for SAW devices[J]. Piezoelectrics & Acoustooptics,2011,33(4):517-519.

- [4] 唐代华,金中,司美菊,等. SAW 滤波器 WLP 封装中腔体抗模压塌陷研究[J]. 压电与声光,2021,43(1):84-87.

TANG Daibua, HN, Zhong, SI, Meiju, et al. Study, op-

- TANG Daihua, JIN Zhong, SI Meiju, et al. Study on-cavity collapse resisting molding pressure in WLP of SAW filter[J]. Piezoelectrics & Acoustooptics, 2021, 43(1):84-87.

- [5] 刘娅,马晋毅,孙科,等. 基于裸芯片覆膜的一款薄膜体声波滤波器[J]. 压电与声光,2021,43(3):299-302. LIU Ya,MA Jinyi,SUN Ke,et al. Anair-gap thin film bulk acoustic resonator filter with laminated film bare die[J]. Piezoelectrics & Acoustooptics, 2021, 43(3): 299-302.

- [6] WILKINS B. Wafer level packaging of SAW enables low cost 2. 5G and 3G radio modules [C]//[S. l.]: Third International Symposium on Coustic Wave Devices for Future Communication Sytem, 2007.

- [7] 杜波,马晋毅,蒋欣,等. 薄膜体声波谐振器有限元仿真与设计[J]. 压电与声光,2016,38(4):531-534.

DU Bo, MA Jinyi, JIANG Xin, et al. Finite element simulation and design of film bulk acoustic wave resonator[J]. Piezoelectrics & Acoustooptics, 2016, 38 (4):531-534.