Aug. 2024

文章编号:1004-2474(2024)04-0505-06

**DOI:** 10. 11977/j. issn. 1004-2474. 2024. 04. 015

# 用于E型薄膜制备的双掩膜工艺研究

郝一鸣1,雷程1,王涛龙1,2,余建刚1,冀鹏飞1,闫施锦1,梁庭1

(1. 中北大学 省部共建动态测试技术国家重点实验室,山西 太原 030051; 2. 成都天奥电子股份有限公司,四川 成都 610037)

摘 要:在高温压力传感器中,与 C 型膜片相比, E 型膜片的稳定性强,非线性误差小,相同挠度下灵敏度高。在微机电系统(MEMS)工艺流程中薄膜制备较重要,其形貌结构对传感器的性能影响较大。但 E 型薄膜的制备过程较难,为制备出形貌良好的 E 型(硅岛)薄膜,采用深反应离子刻蚀机,以 SF<sub>6</sub> 为主要刻蚀气体,通过改变掩模材料对制备工艺进行优化改进,使用共聚焦显微镜和扫描电子显微镜(SEM)对刻蚀后的形貌进行表征。实验表明,通过使用 ROL-7133 负胶和 SiO<sub>2</sub> 双掩膜,前烘 90 s,中烘 120 s,显影 50 s,得到了硅岛高度为 50  $\mu$ m、背腔深度为 450  $\mu$ m 的 E 型薄膜,垂直度较高且整体形貌较好,符合传感器制作要求。

关键词:双掩膜;E型薄膜;深反应离子刻蚀;刻蚀比;刻蚀形貌

中图分类号:TN384;TP212 文献标识码:A

## Study on the Double Mask Process for Preparation of E-Type Films

$\begin{array}{c} \textbf{HAO Yiming}^1 \text{ , } \textbf{LEI Cheng}^1 \text{ , } \textbf{WANG Taolong}^{1,2} \text{ , } \textbf{YU Jiangang}^1 \text{ , } \textbf{JI Pengfei}^1 \text{ ,} \\ \textbf{YAN Shijin}^1 \text{ , } \textbf{LIANG Ting}^1 \end{array}$

State Key Laboratory of Dynamic Measurement Technology, North University of China, Taiyuan 030051, China;

Chengdu Spaceon Electronics Co., Ltd., Chengdu 610037, China)

Abstract: In high-temperature pressure sensors, the E-type diaphragm offers advantages such as strong stability, minimal nonlinear error, and higher sensitivity under the same deflection compared to the C-type diaphragm. The preparation of thin films is crucial in the MEMS process, given that their morphology and structure greatly influence sensor performance. However, there are several challenges in preparing E-type thin films. To produce E-type (silicon island) thin films with good morphology, a DRIE deep reactive ion etching machine was used with SF<sub>6</sub> as the main etching gas. The preparation process was optimized and improved using changing the mask material, and the morphology after etching was characterized using confocal microscopy and scanning electron microscopy (SEM). Experiments showed that using ROL-7133 negative adhesive and a SiO<sub>2</sub> double mask, with pre-drying for 90 s, mid-drying for 120 s, and developing for 50 s, resulted in E-type films with a silicon island height of 50  $\mu$ m and a back cavity depth of 450  $\mu$ m. These films exhibited high perpendicularity and good overall morphology, meeting the requirements for sensor production.

Key words: double mask; E-type film; deep reactive ion etching; etching ratio; etching morphology

## 0 引言

传统的硅压阻式压力传感器芯片通常为 C 型 (方形平板) 膜片,设计和制造过程相对简单。然而随着军工等尖端产业的发展,要求高精度测量。因此,需要进一步提高芯片的灵敏度,可以通过使用面积更大、厚度更薄的平面膜片来实现。但这种方法会迅速增加膜片的挠度,使芯片的线性度变差。

仅增加膜片的长度或减小其厚度来同时提高传感器的灵敏度和线性度难度较大[1-2]。而 E 型薄膜传感器的薄膜设计能够在高温环境下提供更好的力学稳定性和均匀的应力分布,提高了传感器的灵敏度和精度。由于其高温适应性,E 型薄膜压阻式压力传感器广泛应用于需要高温压力监测的场合,如发动机监测、高温流体控制及工业炉压监测等[3]。

收稿日期:2024-03-28

基金项目:国家重点研发计划资助项目(2023YFB3209100);中央引导地方科技发展资金资助项目(YDZJSX20231B006);山西省重点研发计划资助项目(202302030201001)

作者简介:郝一鸣(1997-),女,吉林省长春市人,硕士生。通信作者:梁庭,教授,博士。

通过刻蚀工艺制备 E 型薄膜具有一定难度。刻蚀过程中需要保持高选择性,确保只刻蚀目标区域,避免对邻近区域造成损伤。此外,精确控制刻蚀深度和剖面很重要。因此,设计 E 型膜片并优化其制备工艺,有利于提高传感器的灵敏度和线性度。本文分析总结 E 型薄膜制备过程中遇到的问题,提出了采用双掩膜制备薄膜的方法。采用深反应离子刻蚀机,以 SF。为主要刻蚀气体,通过改变掩膜材料对 E 型薄膜进行刻蚀实验。通过实验找到了较合适的双掩膜材料,刻蚀的 E 型薄膜形貌较好,为 E 型薄膜压力芯片的制作提供了参考。

#### 1 方法

## 1.1 E型膜片设计原理

单晶硅的弹性模量是 165 GPa, 泊松比是 0.28, 破坏应力是  $7 \times 10^8$  N/m²。为了确保在实际工作中遇到超出正常负荷的情况时能够安全运行,实现过载保护,最大允许工作应力为 0.33 $\sigma_m$ ( $\sigma_m$  为最大应力)。分析时,考虑灵敏度、非线性误差及可承受的最大应力等因素,结合小变形理论和过载保护理论进行了分析,可得[ $^4$ ]:

$$\begin{cases} \frac{\Delta R}{R} = \frac{U_{\text{out}}}{U_{\text{in}}} = \frac{0.308}{2} \pi_{44} P \frac{l^{2}}{h^{2}} (1 - v^{2}) \geqslant 1.0\% \\ w_{\text{max}} = 0.015 \times 2 \frac{P l^{4} (1 - v)^{2}}{E h^{3}} \leqslant \frac{1}{5} h \end{cases}$$

$$F_{\text{max}} = 0.308 P_{\text{max}} \frac{l^{2}}{h^{2}} (1 - v) \leqslant 33\% \sigma_{\text{m}}$$

$$(1)$$

式中:l 为 E 型膜片的边长;h 为 E 型膜片的厚度; $w_{\text{max}}$  为 E 型膜片中心的最大位移; $F_{\text{max}}$  为可承受的最大应力; $P_{\text{max}}$  为过载压力;P 为作用于芯片上的实际压力。

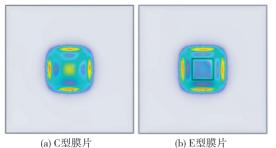

本文薄膜膜片边长为 1 000 mm, 膜厚为 50 mm。 在膜片上施加 l MPa 压力载荷, 得到薄膜上应力分 布如图 1 所示。

(a) C型膜片 (b) E型膜片 (b) E型膜片 图 1 1 MPa 压力下膜片应力分布图

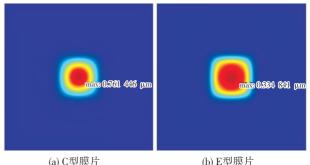

有限元分析软件的结果显示,应力集中区出现在膜片边缘的中心区域,将电阻条放置在此位置可获得最高灵敏度。同时,膜片中心位置也是最大应变所在位置,如图 2 所示。E 型膜片中心最大应变小于 C 型膜片中心最大应变的 1/2。E 型膜片有效地限制了膜片中心区域的应变,可减小非线性误差,从而提高测量的准确性。

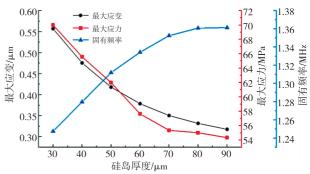

E型结构中位于膜片中心的硅岛作用较大,它通过增加膜片中部的厚度强化其结构,进而提高中心区域的刚度。确保不影响应力集中区域的同时,有效地控制膜片中心的应变,以改善非线性误差。图 3 为不同质量块厚度对可动膜片机械性能的影响。由图可知,随着硅岛厚度的增加,E型膜片的最大应力和最大应变均呈下降趋势,而膜片的固有频率则呈上升趋势。为了平衡传感器的线性度和固有频率,需合理选择质量块厚度。最后确定中心质量块长宽均为 500 μm,厚为 50 μm。

图 3 不同质量块厚度对可动膜片机械性能的影响

## 1.2 深反应离子刻蚀(DRIE)工艺

E型膜压阻式压力传感器敏感芯片需通过背腔刻蚀形成敏感结构,利用硅的深刻蚀工艺实现背腔刻蚀。常用的刻蚀工艺有湿法工艺、低温工艺、混合气体工艺和 Bosch 工艺。在湿法工艺中,图形保真效果不理想,刻蚀图形的最小线宽掌控难,且垂直度低。低温工艺刻蚀速率低,在长时间的刻蚀过

程中光刻胶可能会开裂。对于涉及混合 SF<sub>6</sub>/C<sub>4</sub>F<sub>8</sub> 或其他刻蚀和钝化气体(SF<sub>6</sub>/CHF<sub>3</sub>)的混合气体工艺,其主要缺点是硅和光刻胶的低选择性(4:1)和低刻蚀速率(150 nm/min)。1996 年,Laermer 和Schilp 发明了一种钝化和刻蚀交替的工艺,展现了DRIE 的全部潜力。将物理和化学刻蚀成功地结合在一起,具有高控制精度、高选择性等优点,能够实现高深宽比的刻蚀结构,即刻蚀深度与特征尺寸之比很大,同时能保持侧壁的垂直度和均匀性[5-7],因此成为微机电系统(MEMS)加工技术中进行硅深度刻蚀的理想选择。

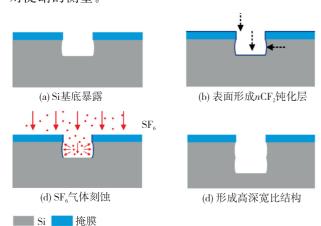

Bosch 工艺的刻蚀过程(见图 4)通常分为刻蚀和钝化两个阶段。每次沉积都会在整个平面上形成一层钝化膜,所以在刻蚀过程中,物理刻蚀所用的等离子体主要是物理轰击垂直方向上的材料,而实现其刻蚀。因此,侧壁得到保护,从而形成了相对陡峭的侧壁。

图 4 刻蚀过程原理图

在 Bosch 工艺中,刻蚀、钝化气体分别为六氟化硫( $SF_8$ )及八氟环丁烷( $C_4F_8$ )。首先在反应室内充满  $C_4F_8$  气体, $C_4F_8$  在等离子体中形成氟化碳类高分子聚合物,沉积在硅表面阻止氟离子与硅反应,形成保护层,防止侧向刻蚀的发生。钝化方程为

$$\begin{cases} C_4 F_8 + e^- \rightarrow CF_x^+ + CF_x^- + F^- + e^- \\ CF_x^- \rightarrow n CF_2 \end{cases}$$

(2)

钝化过程如图 4(b)所示。其次在反应室内通入 SF<sub>6</sub> 气体进行刻蚀,刻蚀方程为

$$\begin{cases} nCF_2^+ + F^- \rightarrow CF_x^- \rightarrow CF_2 \uparrow \\ SF_6 + e^- \rightarrow S_x F_y^+ + S_x F_y^- + F^- + e^- \\ Si + F^- \rightarrow SiF_x \end{cases}$$

(3)

F<sup>-</sup>与钝化膜发生反应产生挥发性气体 CF<sub>2</sub>,从

而对暴露出的硅基部件进行刻蚀。另外, Si 和钝化层被轰击进行物理刻蚀, 刻蚀工艺和钝化沉积工艺间快速交替形成具有垂直侧壁的刻蚀轮廓<sup>[8]</sup>。

Bosch 工艺刻蚀速度快,深宽比高,选择比好, 因而形成了 DRIE 工艺的一个典型特征——扇形侧壁,Bosch 工艺产生的独特扇形是不可避免的,由于 在纳米级,其影响可忽略。

本文采用英国 SPTS 公司生产的型号 Omega LPX Dsi 的深反应离子刻蚀机(见图 5),该刻蚀系统可用于高深宽比硅结构的刻蚀。

图 5 深反应离子刻蚀机

## 2 实验过程及分析

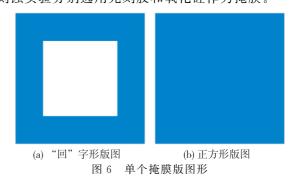

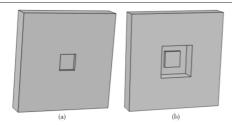

掩膜应选择价格低、易集成及去除,且应具有高刻蚀选择比,对 DRIE 设备无污染。掩膜材料一般选择氧化物、金属和光刻胶,其具备较高的刻蚀选择比。在使用过程中,金属掩膜可能会在设备刻蚀腔体中留下污染物,影响刻蚀形貌和刻蚀效果[9-12]。E型薄膜的刻蚀需要进行套刻,掩膜版图如图 6 所示。第一次刻蚀为"回"字形版图,形成中间硅岛。第二次刻蚀为正方形版图,进行腔体整体刻蚀,最后形成 E型薄膜(见图 7),故第二次刻蚀掩膜的选择需慎重考虑。在选择掩膜材料时,综合考虑其优点和可能带来的负面影响后,本次单层掩膜刻蚀实验分别选用光刻胶和氧化硅作为掩膜。

图 7 E型薄膜刻蚀结构形状

实验采用样品是直径为 $\emptyset$ 4 in(1 in=2.54 cm)、电阻率为  $0.001\sim0.005~\Omega/\text{cm}$ 、晶向为 $\langle 100\rangle$ 、厚度为  $500~\mu\text{m}$  的单晶硅晶圆。实验前,取硅晶圆样品分别通过 3 号液( $\varphi$ ( $H_2SO_4$ ): $\varphi$ ( $H_2O_2$ )=3:1)加热至 150~%清洗 15~min,使用去离子水喷淋冲洗 5~X,随后再放入 1 号液( $\varphi$ ( $NH_3$  •  $H_2O$ ): $\varphi$ ( $H_2O_2$ ): $\varphi$ ( $H_2O$ )=1:2:7)加热至 60~%清洗 5~min,使用去离子水进行 5~X 恢沸冲洗后,将其取出并使用氮气进行吹干处理,等待实验。

#### 2.1 光刻胶掩膜刻蚀 E 型薄膜

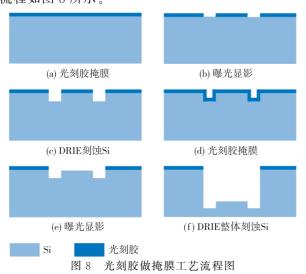

常规刻蚀工艺通常选用 AZ6130 光刻胶,厚度可达 5  $\mu$ m。本文实验刻蚀深度较大,需选择更厚光刻胶作为掩膜,满足刻蚀中的掩膜消耗。因此,本文选择国产 RDP-2100P 型正胶(厚度达 9~11  $\mu$ m)。第一步刻蚀掩膜使用 RDP-2100P 型正胶,旋涂光刻胶,经过前烘 1 min 预处理、曝光、25%四甲基氢氧化铵(TMAH)溶液与水体积配比 1:8 进行稀释,显影 120 s、镜检、氧等离子体扫底膜去除残余浮胶、后烘 10 min 坚膜等标准图形化工艺,使得光刻胶具有掩膜作用,再使用 Omega LPX Dsi 的深反应离子刻蚀机进行刻蚀。第二步刻蚀掩膜同样使用 RDP-2100P 型正胶,经标准图形化工艺后进行刻蚀,工艺流程如图 8 所示。

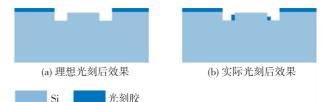

刻蚀完成后,在共聚焦显微镜下观察刻蚀情况,如图 9 所示。由图可看出,硅岛四周均有未被刻蚀完全的残留物,且高度不一。经分析,其原因是第二次光刻时,光不能保证完全照射到硅岛侧面,尤其是侧面下侧,硅岛侧面未完全曝光,显影后侧面仍有光刻胶残留(见图 10),故刻蚀不完全。

图 9 光刻胶掩膜刻蚀 E 型薄膜共聚焦图像

图 10 理想与实际光刻后效果对比图

#### 2.2 SiO, 掩膜刻蚀 E 型薄膜

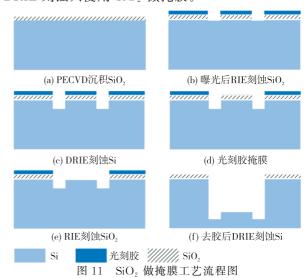

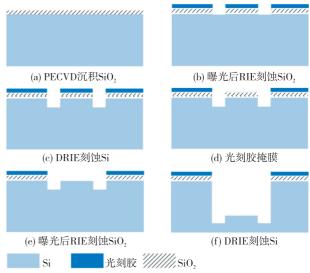

SiO<sub>2</sub> 薄膜性能稳定,可用作刻蚀掩膜。工艺流程如图 11 所示。在晶圆表面依次感应耦合等离子体化学气相沉积(ICP-CVD)生长  $1~\mu m$  SiO<sub>2</sub>、涂覆RDP-2100P型光刻胶作为掩膜,第一次曝光后先进行RIE 刻蚀掉 SiO<sub>2</sub>(RIE 刻蚀 SiO<sub>2</sub>后,将晶圆放置缓冲氧化物刻蚀液(BOE)中 2~s,以确保 SiO<sub>2</sub> 被完全去除),暴露出 Si 基底再进行 DRIE 刻蚀;第二次刻蚀仍先使用 RDP-2100P型光刻胶做掩膜,曝光后RIE 刻蚀掉 SiO<sub>2</sub>,然后通过丙酮、乙醇溶液各超声洗 5~min,去除光刻胶,如图 11(f)所示。第二次DRIE 刻蚀只使用 SiO<sub>2</sub>。做掩膜。

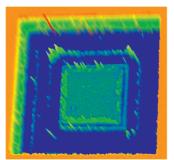

刻蚀完成后,在共聚焦显微镜下观察刻蚀情况,如图 12 所示。由图可看出,刻蚀底面平整度较低,光刻胶掩膜实验硅岛侧面刻蚀情况改善,但仍有少量残留,并且在距离硅岛约 40 mm 处,四周出现一圈有少量残留的、未被刻蚀完全的凸起。如图 13 所示,因刻蚀深度较大,刻蚀时间较长,SiO<sub>2</sub> 掩膜被侵蚀,在刻蚀过程中,被侵蚀的 SiO<sub>2</sub> 覆盖在需被刻蚀的底部,形成新的掩膜,从而造成少量刻蚀残留。

图 12 SiO<sub>2</sub> 掩膜刻蚀 E 型薄膜共聚焦图像

图 13 SiO。掩膜被侵蚀

#### 2.3 双掩膜刻蚀 E 型膜片

由单层掩膜实验结果及分析可知,RDP-2100P型正胶掩膜显影后硅岛侧壁有残留,SiO<sub>2</sub>掩膜被侵蚀并造成底部刻蚀不完全,以上方法无法满足 E型薄膜的制备。为排除以上因素影响,本文采用双掩膜进行刻蚀实验。底层仍使用 SiO<sub>2</sub> 掩膜,上面覆盖光刻胶作牺牲保护层,防止 SiO<sub>2</sub> 被侵蚀而影响刻蚀。修改掩膜版,使用 ROL-7133 型负胶,其粘附性好、胶厚适中,且利用负性胶曝光区间得到保留及在未曝光区间显影的性质,以消除硅岛侧壁光刻胶未被完全曝光而残留的影响。

工艺流程图如图 14 所示。第一次刻蚀步骤同以上  $SiO_2$  掩膜刻蚀实验,第二次刻蚀使用 ROL-7133 型负胶,在晶圆表面喷涂 2 圈光刻胶,厚度约7.5  $\mu$ m,经过前烘 90 s 预处理、曝光、中烘 120 s,25% TMAH 溶液配比 1: 10 显影 50 s、镜检、氧等离子体扫底膜去除残余浮胶、后烘 120  $\mathbb{C}$ 、10 min

坚膜等标准图形化工艺,使光刻胶具有掩膜作用。如图 14(e)、(f)所示。首先 RIE 刻蚀掉  $SiO_2$ ,然后在不去除顶层光刻胶的情况下进行 DRIE 刻蚀 Si。

图 14 双层掩膜工艺流程图

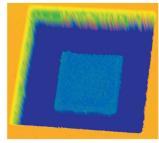

刻蚀完成后,在共聚焦显微镜下观察刻蚀情况,如图 15 所示。由图可看出,硅岛刻蚀完全,四周未出现侧壁残留。为进一步观察刻蚀结果,使用场发射扫描电子显微镜(SEM)对表面形貌进行表征,如图 16、17 所示。由图可看出,刻蚀后的表面光滑,无明显的毛刺状物质,表明刻蚀过程中材料去除均匀,没有造成表面损伤。硅岛边缘清晰,无多余残留,边缘接近垂直于基底(见图 18),达到预期要求。图中, 本为硅岛侧面与底面的夹角, Aa、Rz 代表两条直线重合点。

图 15 光刻胶、SiO<sub>2</sub> 双层掩膜刻蚀 E 型薄膜共聚焦图像

图 16 光刻胶、SiO。双层掩膜刻蚀 E 型薄膜正面 SEM 图像

图 17 光刻胶、SiO。双层掩膜刻蚀 E 型薄膜侧面 SEM 图像

图 18 硅岛侧面与底面角度

## 3 结束语

针对压阻式高温压力传感器中 E 型薄膜制备问题,本文总结了使用常规掩膜刻蚀过程中遇到的套刻时使用正性光刻胶掩膜曝光不完全、SiO₂掩膜被侵蚀、图案边缘刻蚀不完全等问题,通过选择合适的掩膜,即 SiO₂和 ROL-7133型负胶双掩膜,制备出硅岛高 50 μm、背腔深 450 μm 的 E 型薄膜,最终实现了压阻式高温压力传感器的薄膜制备。通过共聚焦显微镜及场发射扫描电子显微镜观测表明,薄膜形貌良好,垂直度较高,符合压阻式高温压力传感器的制备要求。

## 参考文献:

- [1] 吴佐飞,尹延昭,田雷,等.一种压阻式微压传感器芯片设计与实现[J]. 传感器与微系统,2018,37(6):3. WU Zuofei,YIN Yanzhao,TIAN Lei,et al. Design and implementation of a piezoresistive micropressure sensor chip[J]. Sensors & Microsystems,2018,37(6):3.

- [2] LI C, CORDOVILLA F, OCANA J L. Annularly grooved mem-brane combined with rood beam piezoresistive pressure sensor for low pressure applications [J]. Review of Scientific Instrument, 2017, 88:035002.

- [3] 李闯,赵立波,张磊,等. 基于 SOI 的 E 型结构 MEMS 压力芯片优化设计与制造[J]. 传感器与微系统,2020,39(4):73-76.

LI Chuang,ZHAO Libo,ZHANG Lei, et al. Optimized

- design and fabrication of E-structure MEMS pressure chips based on SOI[J]. Sensors & Microsystems, 2020,39(4):73-76.

- [4] 李闯,赵立波,王尊敬,等.基于 SOI 的 E 型膜结构耐高温压力芯片的设计与制造[J]. 仪表技术与传感器, 2021(1):20-24.

- LI Chuang, ZHAO Libo, WANG Zunjing, et al. Design and fabrication of high-temperature pressure-resistant chips with E-type membrane structure based on SOI [J]. Instrumentation Technology and Sensors, 2021 (1):20-24.

- [5] 颜改革,韩敬宁,殷志富,等. 硅基深宽比结构与  $SiO_2$  薄膜的干法刻蚀方法研究[J]. 仪表技术与传感器, 2015(11):1-3.

- YAN Gaige, HAN Jingning, YIN Zhifu, et al. Dry etching method of silicon-based aspect ratio structure and  $SiO_2$  film [J]. Instrumentation Technology and Sensors, 2015(11):1-3.

- [6] 周仑. 硅基深刻蚀的工艺研究[D]. 武汉:华中科技大学,2019.

- [7] 卢雪怡. 基于 DRIE 工艺的太赫兹透镜天线关键技术研究[D]. 南京:东南大学,2022.

- [8] TILLOCHER T, NOS J, ANTOUN G, et al. Comparison between Bosch and STiGer processes for deep silicon etching[J]. Micromachines, 2021,12:1143.

- [9] HONG Tijing, LIU Dengfeng, LIU Yi'an. Radar active jamming recognition based on multiscale fully convolutional neural network and GRU[J]. Computer Science, 2024, 51(5):306-312.

- [10] 冀鹏飞,赵妍琛,雷程,等. 硅压敏电阻刻蚀形貌对高温压力传感器输出特性影响[J]. 仪表技术与传感器,2023(12):10-15.

- JI Pengfei, ZHAO Yanchen, LEI Cheng, et al. The influence of silicon varistor etching topography on the output characteristics of high-temperature pressure sensors[J]. Instrumentation Technology and Sensors, 2023(12):10-15.

- [11] WANG Chundong, LI Quan, FU Haoran, et al. Face anti-spoofing method with adversarial robustness[J]. Computer Science, 2024, 51(6A): 230400022-7.

- [12] 关一浩,雷程,梁庭,等. RIE 反应离子刻蚀氮化硅工艺的研究[J]. 电子测量技术,2021,44(7):107-112. GUAN Yihao, LEI Cheng, LIANG Ting, et al. Research on the process of ionic etching of silicon nitride by RIE[J]. Journal of Electronic Measurement Technology,2021,44(7):107-112.